- Positive negative edge triggered flip flop verilog verification#

- Positive negative edge triggered flip flop verilog code#

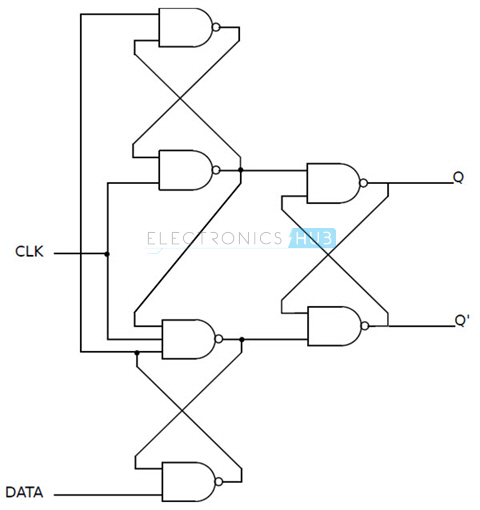

Nand_g nand_2(y, clk_in, dbar) /NAND gate module is called with y, clk_in and dbar parameter Nand_g nand_1(x, clk_in, d_in) /NAND gate module is called with x, clk_in and d_in parameter Not_g not_1(dbar, d_in) /NOT gate module is called with dbar and d_in parameter Output q_out, qbar_out / output of the D flip flop q_out and qbar_out where q_out and qbar_out is compliment to each other Input d_in, clk_in / input variable of D flip flop d_in is the data input and clk_in is the clock input * this module defines a d flip flop which will be design with NAND gate and NOT gate *// Module d_ff_st(q_out, qbar_out, d_in, clk_in ) Output e / e is the output variable of the NOT gate Input f / f is the input variable to the NOT gate Module not_g(e, f) / this block defines the NOT gate Output c / output variable of NAND gate is definedĪssign c = ~(a & b) / this assign is used to derive the value of c through a and bĮndmodule /module end with endmodule statement

Input a, b / a and b is the input variable to the NAND gate

Positive negative edge triggered flip flop verilog code#

Verilog Code for D flip flop using NAND gates module nand_g(c, a, b) //*each module contains statements that defines the circuit, this module defies a NAND gate which is named as nand_g*// Here, all the code is designed with D flip flop whether VHDL or Verilog code.

Positive negative edge triggered flip flop verilog verification#

Verilog was originally for stimulation and verification of digital circuits, it is a hardware description language (HDL). VHDL Code for Asynchronous Counter using D flip flop.VHDL Code for 8 bit Register using D flip flop.4 bit Shift Register using D flip flop VHDL Code.VHDL Code for Negative Edge Triggered D flip flop.VHDL Code for D flip flop with Synchronous Reset.VHDL Code for D flip flop with Asynchronous Reset.VHDL Code for D flip flop using Structural Model.VHDL Code for D flip flop using Dataflow Modelling.Frequency Divider using D flip flop Verilog Code.JK flip flop using D flip flop Verilog Code.Verilog Code for T flip flop using D flip flop.V erilog Code for Ring Counter using D flip flop.Verilog Code for D flip flop using Structural Model.Negative Edge Triggered D flip flop Verilog Code.Positive Edge Triggered D flip flop Verilog Code.4 bit Ripple Counter using D flip flop Verilog Code.4 bit Shift Register using D flip flop Verilog Code.Verilog Code for D flip flop using Dataflow Modelling.Verilog Code for D flip flop using NAND gates.

0 kommentar(er)

0 kommentar(er)